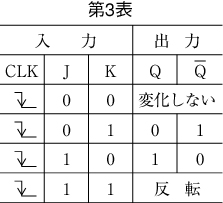

組合せ回路は、ある入力信号によって信号が出力され、入力信号が取り去られると元の状態に戻る。フリップフロップ回路は、組合せ論理回路の一つであるが、入力信号を取り去っても、その出力状態を維持し続ける。このためフリップフロップ回路は、ラッチ(留め金という意味)回路とも呼ばれる。

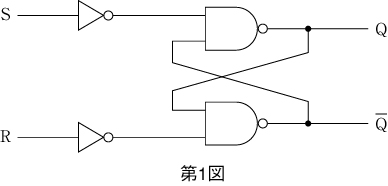

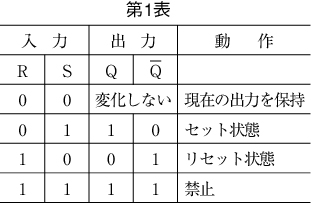

最も基本的なフリップフロップ回路を第1図に示す。この回路は、二つの入力信号によって、その出力状態をリセット(Reset)された状態またはセット(Set)された状態に保持する。この回路をRS‐フリップフロップ(RS‐Flip‐Flop:以下、RS‐FFと略する)回路という。RS‐FF回路は、基本的なラッチ回路である。

RS−FF回路には、 ![]() と

と ![]() の二つの出力端子が設けられ、互いに逆の信号を出力する。つまり、

の二つの出力端子が設けられ、互いに逆の信号を出力する。つまり、 ![]() =1のときは

=1のときは![]() =0、

=0、 ![]() =0ときは

=0ときは ![]() =1になる。RS‐FF回路の真理値表を第1表に示す。

=1になる。RS‐FF回路の真理値表を第1表に示す。

このRS‐FFの動作を公園で見掛けるシーソにたとえると分かりやすい。シーソの両端の一方側をセット、反対側をリセットとする。この場合、セット側に力を加えるとシーソは傾き、力を離してもシーソはその状態を維持して安定する。今度はシーソの反対側に力を加えるとシーソはその方向に傾き、力を与えなくてもシーソは同様にその状態を維持して安定する。ところが、セット側とリセット側の両方に力を加えるとどちらにも落ち着かず不安定な状態になる。これと同じようにRS‐FFのセットとリセットの両方を1にすると、フリップフロップとして機能しなくなるので両方とも1にする入力を禁止している。

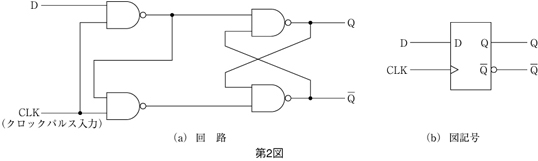

RS‐FFは、RとSを同時に1にするとフリップフロップとしての機能を失う。このため第2図に示すようにクロックパルス入力を設けて、このときに入力された値を出力して保持するように構成したラッチ回路がある。この回路をD‐FF(遅延形‐FF:Delay‐FF)という。D‐FFの動作を第2表の真理値表に示す。

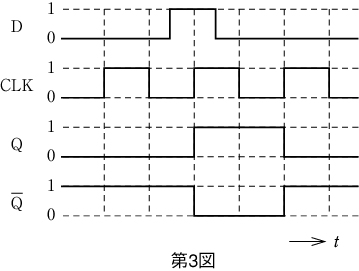

D-FFの動作を示すタイムチャートを第3図に示す。タイムチャートによれば、クロックパルスが入力されたときのD端子の入力信号の状態が入力信号を取り去っても、出力端子に保持されることが分かる。

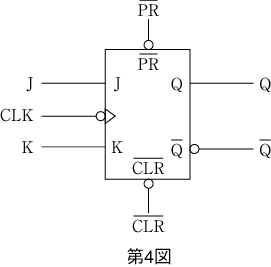

前述のD‐FF及びJK‐FFはクロックパルスが入力された時点で出力が変化するが、一般的にD‐FFはクロックパルスが0から1になったとき出力が変化し、JK‐FFはクロックパルスが1から0になったときに出力が変化するものが多い。

また、D‐FFとJK‐FFにはクロックパルスによらず、出力を直接リセットまたはセットする端子が設けられている。例えば第4図に示すJK‐FFの図記号で CLR端子がリセット、 PR端子がセットに相当する。

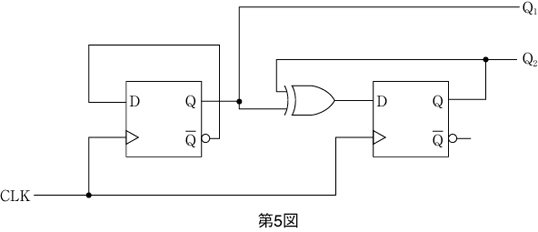

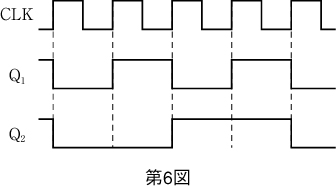

ディジタル回路で扱う1または0の数を計数する回路をカウンタと呼ぶ。このカウンタはフリップフロップを組み合わせて作ることができる。例えば、第5図に示す回路は4進カウンタと呼ばれる。この回路はクロックパルスが入力される度に二つのFFの出力 ![]() 1、

1、 ![]() 2が(

2が( ![]() 2,

2, ![]() 1)=(0,0)→(

1)=(0,0)→( ![]() 2,

2, ![]() 1)=(0,1)→(

1)=(0,1)→( ![]() 2,

2, ![]() 1)=(1,0)→(

1)=(1,0)→( ![]() 2,Q1)=(1,1)→(

2,Q1)=(1,1)→( ![]() 2,

2, ![]() 1)=(0,0)→・・・と4通りに順番に変化する。このようにクロックパルスが入力される度にその出力状態が4通りに変化するので4進カウンタと呼ばれる。

1)=(0,0)→・・・と4通りに順番に変化する。このようにクロックパルスが入力される度にその出力状態が4通りに変化するので4進カウンタと呼ばれる。

| (A) | (B) | (C) | (D) |

| (1) | b | b | b | a |

| (2) | b | a | b | b |

| (3) | a | a | b | a |

| (4) | a | b | a | b |

| (5) | a | a | a | b |

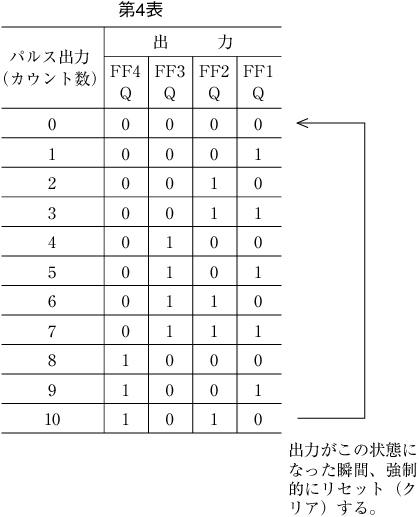

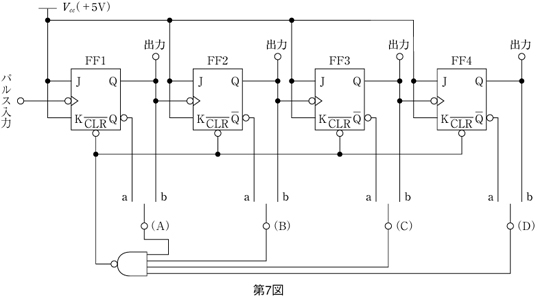

[解説]10進カウンタの真理値表を第4表に示す。この表に示されるようにパルスが入力される度にカウンタが一つずつ増加していく。10進カウンタは10個の状態を繰り返していくので、カウンタの出力は0〜9までとなる。 非同期10進カウンタはカウンタが10になった瞬間に0000にカウンタをリセットして初期状態に戻る。以後、パルスが入力されるたびにカウンタが一つずつ増加を繰り返す。

[答](4)